"Europe will not be made all at once, or according to a single plan. It will be built through concrete achievements which first create a de facto solidarity." Robert Schuman

# **KDT JU**

## **KDT-CY WORKSHOP ON CALL 2022**

Yves GIGASE

**Head of Programmes**

KDT-CY workshop 29 July 2022

1

KDT JU 2021-2027

- Third generation JU (start 30/11/2021), predecessor was ECSEL JU

- KDT JU = Key Digital Technology Joint Undertaking

- Tripartite: Commission Participating states Industry associations

- Associations: AENEAS, INSIDE, EPoSS

- Budget ambition: 7.2B€ funded by 1,8 B€ (EU)+1,8 B€ (national)

- · Based on Horizon Europe

- Bottom-up programme with top-down focus topics

- "Value chain" approach

- Pilot lines (higher TRLs)

- · Critical mass approach

- focussed on Industrial leadership

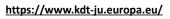

- Common agenda of Europe's ECS community

Yves Gigase KDT-CY workshop, 29 July 2022

**Participating**

#### THE EU RD&I FUNDING LANDSCAPE FOR THE ECS INDUSTRY

## **ECSEL JU 2014-2021**

- 92 projects

- 3 220 beneficiaries

- 4 690 million Eur in total cost

- 2 280 million Eur in funding (EU+national)

- 408 500 persons-months

- 34 000 person-years

- 29 participating states

No participation from Chypriot organizations

Yves Gigase KDT-CY workshop, 29 July 2022

EUROPEAN PARTNERSHIP

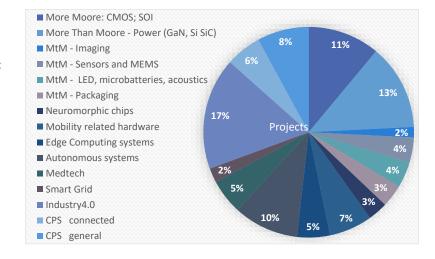

## **ECS SRIA**

- Boost industrial competitiveness through interdisciplinary technology innovations.

- Ensure/reinforce EU strategic autonomy through secure, safe and reliable ECS supporting key European application domains.

- Establish and strengthen sustainable and resilient ECS value chains supporting the Green Deal.

- Unleash the full potential of intelligent and autonomous ECS-based systems for the European digital era.

Yves Gigase KDT-CY workshop, 29 July 2022

EUROPEAN PARTNERSHIP

5

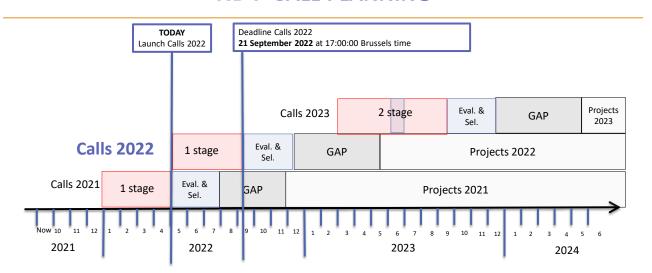

#### **KDT CALL PLANNING**

Yves Gigase KDT-CY workshop, 29 July 2022

EUROPEAN PARTNERSHIP

#### **A WORD OF CAUTION**

Check regularly our call website under the KDT website:

www.kdt-ju.europa.eu

Changes in National conditions are to be expected!

Contact email for your questions (please use ONLY this email): calls@kdt-ju.europa.eu

But for every IT issue contact the IT helpdesk (link in participant portal). We cannot help you on IT issues!

Yves Gigase KDT-CY workshop, 29 July 2022

7

### WHAT IS NEW? WHAT IS DIFFERENT?

H2020 very similar to Horizon Europe for calls

KDT Call 2022 very similar to previous ECSEL calls (eg Call 2020)!

But there are differences!!!!

Therefore read the sections on the calls in the Work Plan 2022, read the documents, etc.

EUROPEAN PARTNERSHIP

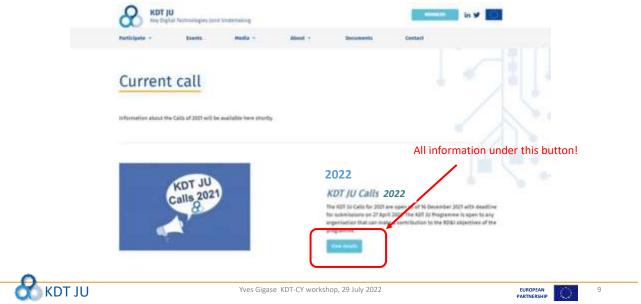

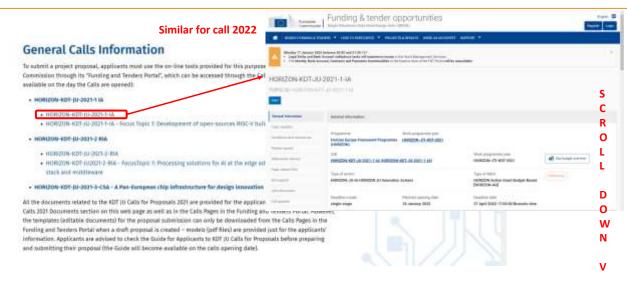

## How to START? GO TO KDT CALL WEBPAGE!

#### STRUCTURE AND TOPICS

#### KDT JU opens 2 concurrent Calls in 2021

- · HORIZON-KDT-JU-2021-1 IA

- HORIZON-KDT-JU-2021-1-IA

- . HORIZON-KDT-JU-2021-1-IA Focus Topic 1: Development of open-sources RISC-V building blocks

- HORIZON-KDT-JU-2021-2 RIA

#### Similar for 2022

- · HORIZON-KDT-IU-2021-2-RIA

- . HORIZON-KOT-JU2021-2-RIA FocusTopic 1: Processing solutions for Al at the edge addressing the design stack and middleware.

- · HORSZON-KDT-JU-2021-3-CSA A Pan-European chip infrastructure for design innovation

#### Who can participate?

The KDT JU Programme is open to any organisation that can make a contribution to the RD&I objectives of the programme. However, there are specific eligibility criteria relevant in the each KDT JU Participating State; these are listed in the KDT JU Work Programme 2021 (see below).

Yves Gigase KDT-CY workshop, 29 July 2022

#### STRUCTURE AND TOPICS

#### 2 calls, 3 focus topics

| Action         | Topic                                                 |

|----------------|-------------------------------------------------------|

| Call 2022-1 T1 | Topic 1 General according to SRIA 2022 (IA)           |

| Call 2022-1 T2 | Topic 2: Focus topic on Industrial supply chain for   |

|                | silicon photonics (IA)                                |

| Call 2022-1 T3 | Topic 3: Focus topic on Design of Customisable and    |

|                | Domain Specific Open-source RISC-V Processors (IA)    |

| Call 2022-2 T1 | Topic 1: General according to SRIA 2022 (RIA)         |

| Call 2022-2 T2 | Ttopic 2: Focus topic on Ecodesigned smart electronic |

|                | systems supporting the Green Deal objectives (RIA)    |

|                | Total                                                 |

Yves Gigase KDT-CY workshop, 29 July 2022

11

11

#### FOCUS TOPIC ON INDUSTRIAL SUPPLY CHAIN FOR SILICON PHOTONICS (IA)

Overall strategy: goal to set up an industrial manufacturing capability for current and next generation silicon photonic integrated circuits and including the various elements of the value chain such as packaging of those PIC-components. In parallel also develop agile heterogeneous PIC platforms of separately manufactured components or CMOS-uncommon materials onto silicon photonics wafers (wafer-level heterogeneous integration).

Details (some):

- establish an (eventually distributed) **industrially based** (meaning pilot line established in an industrial environment) **pilot line for a silicon photonics manufacturing platform**, that is the pilot line must cover the full process for silicon photonics circuits (including if possible heterogenous integration aspects for PICs) covering front and back end, integration and packaging (SiP) as well as wafer-level-test, chip testing, device testing to industrial standards with special attention to the scalability of the backend packaging and testing.

- enable breakthroughs in silicon PIC platforms, overcoming their current limitations, by wafer-level heterogeneous integration of CMOS-uncommon materials or processed chiplets and prepare the transfer to the industrial silicon manufacturing platform.

- At least two demonstrators should be built including PICs made on the pilot line covering distinctive high volume applications such as LIDAR technology, consumer medical applications, etc.

- etc

- Read the WP2022 section on this topic!

- Please note the added evaluation criterion:

This call shall bring together the ECS community and the Photonics community. A well balanced composition with members of the two communities in the consortium should reflect this. This will be evaluated by the experts in the implementation criterion

Yves Gigase KDT-CY workshop, 29 July 2022

EUROPEAN PARTNERSHIP

# FOCUS TOPIC ON DESIGN OF CUSTOMISABLE AND DOMAIN SPECIFIC OPEN-SOURCE RISC-V PROCESSORS (IA)

#### Overall strategy:

- A. Customizable high-end RISC-V based multi-processor core (including dedicated hardware & supporting software IP, enhanced or new libraries of HW peripherals and software), to be applied for high-end computing or domain-specific applications, including features as a.o. dependability, reliability and security.

- B. Based on A, domain specific adaptations of RISC-V customisable processor solutions for safe, secure and reliable computationally intensive applications, e.g., for automotive and other sectors. Such solutions are expected to address appropriate functional and non-functional, high-performance requirements aiming at realizations on advanced technology, e.g. 22nm FDSOI, 16 nm FinFET or below

#### Details

- foundational RISC V compliant building blocks, both hardware and software, with appropriate models and tools support, for customizable high-end application cores for high-performance embedded systems and/or general purpose HPC processors

- Apply the RISC-V developments and tools towards an industrial application demonstrator down to chip implementation

- · etc.

- Read the WP202 section on this topic!

Yves Gigase KDT-CY workshop, 29 July 2022

13

13

# FOCUS TOPIC ON ECODESIGNED SMART ELECTRONIC SYSTEMS SUPPORTING THE GREEN DEAL OBJECTIVES (RIA)

#### Overall strategy:

- Innovative solutions that demonstrate a reduced environmental footprint, allow full recycling, include repair options or demonstrate significantly increased lifetime or second life concepts of ECS.

- Development of new concepts, metrics and standards to assess and support reduced environmental footprint and sustainability of ECS products.

#### Details:

- Develop innovative design and manufacturing methodologies for smart electronic systems, considering eco-design

principles, including aspects related to life cycle, end-of life, standardisation, certification, easy repair and regulation

compliance. Accessible environmental data repository and exchange framework should also be taken into account.

- Demonstrate that reliability-by-design principles maximise the durability of the smart electronic systems proposed or

else allow second life of electronic components, products or systems in future. Important factors are repair-friendly

product designs, solution to enable predictive maintenance and availability of spare parts, implemented through new

business models.

- Target more efficient recovery and recycling solutions or/and optimisation of the use of resources (i.e. reuse/repair/repurpose, recovery and recycling of waste and materials with a special attention to rare earth metals) over the lifetime of smart electronic systems (for example by appropriate packaging design). Specifications for equipment and systems for sorting, waste stream separation, recycling processes of such electronic components.

#### etc.

· Read the WP202 section on this topic!

Yves Gigase KDT-CY workshop, 29 July 2022

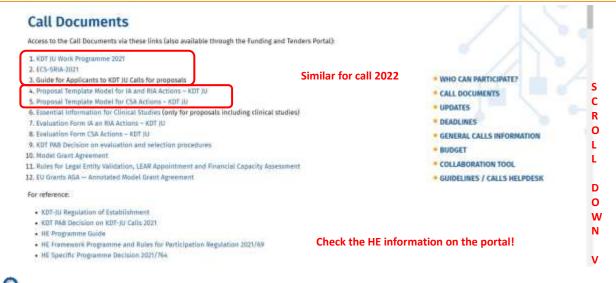

#### **CALL DOCUMENTS**

Yves Gigase KDT-CY workshop, 29 July 2022

EUROPEAN PARTNERSHIP

15

15

#### **UPDATES**

## READY? Go!

Yves Gigase KDT-CY workshop, 29 July 2022

EUROPEAN PARTNERSHIP

17

17

### How to Participate?

#### ECS Collaboration Tool A networking tool for project ideas and potential partners.

inside and AENEAS have now marged their collaboration support tools into a single co-managed service, the ECS Collaboration Tool. AENEAS and Inside Industry Association wented to create one tool to facilitate easy information exchange within the ECS community and allow the

Three industry organisations: **AENEAS INSIDE Industry Association EpoSS**

https://aeneas-office.org/collaboration/ecs-tool/ https://www.inside-association.eu/ https://www.smart-systems-integration.org/

Create a project idea

collection and management of all relevant data, ideas and project proposals in one-place

Look for a partner

tritiate a project idea in the ECS Collaboration Tool, invite partners and browse other project ideas.

Use the partner search on ECS Collaboration Tool to look for possible partners based on their expertise and invite them to join your project idea.

Yves Gigase KDT-CY workshop, 29 July 2022

## **EU FUNDING RATES**

| Type of beneficiary               | IA   | IA Focus<br>Topic | RIA  | RIA Focus<br>Topic |

|-----------------------------------|------|-------------------|------|--------------------|

| Large Enterprise                  | 20 % | 25 %              | 25 % | 25 %               |

| SME                               | 30 % | 35 %              | 35 % | 35 %               |

| University/Other (not for profit) | 35 % | 35 %              | 35 % | 35 %               |

National funding shall be commensurate to the EU funding rates.

Yves Gigase KDT-CY workshop, 29 July 2022

19

19

#### **IMPORTANT DIFFERENCES WITH ECSEL CALLS**

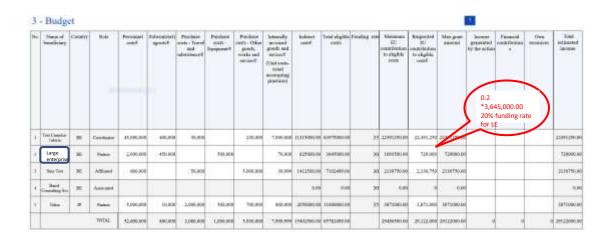

- EU Funding Rates in the Budget table (EU Budget/EU Funding) in the Part A

- National Budgets Table

- National Part (previous Part C)

(Look for detailed instructions in the Guide for Applicants)

PARTN

### FUNDING RATES IN THE BUDGET TABLE IN PART A

Due to limitations of the submission tool the funding rate of the large enterprises is not taken into account in the budget table of the Part A. Therefore, the large enterprises need to check the funding rates they are entitled to in the Work Programme, calculate the EU Funding/contribution outside the portal and fill in the calculated amount in the budget table in the column named "Requested EU contribution to eligible costs"

An example provided below for a large enterprise (LE) participating to the IA call – funding rate 20%; portal indicates 30% (which is for SMEs only). Large enterprise calculates 20% of the total eligible costs and introduces manually the amount in the "Requested EU contribution to eligible costs"

Yves Gigase KDT-CY workshop, 29 July 2022

21

#### FUNDING RATES IN THE BUDGET TABLE IN PART A

EUROPEAN

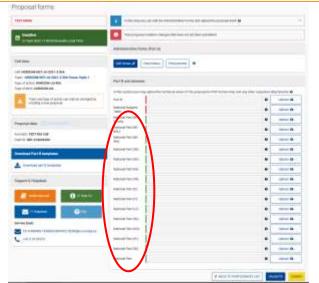

## NATIONAL PART (FORMERLY KNOWN AS PART C)

The previous Part C are now named **National Part** and have a dedicated **Place Holder** for each of the KDT JU Participating State that request such an annex.

Instructions about these annexes are provided in the Annex 3 of the Work Programme of the respective Participating States.

(The name changed in order to avoid the system blockages due to confusion with the Part C which is now dedicated nomenclature in some Horizon Europe programme (dynamic forms which are automatically checked by the system every time a "Part C" name appears.)

Yves Gigase KDT-CY workshop, 29 July 2022

EUROPEAN PARTNERSHIP 0

23

23

#### **NATIONAL BUDGETS TABLE**

(Due to limitations of the submission tool the table for the national funding (eligible costs according to the national rules and national contributions requested) is not anymore integrated in the Part A (Administrative Forms) but has to be submitted separately as am xls file which must be uploaded to the dedicated placeholder named "National Budgets Table")

The template is provided in the "Download Part B template" tab together with the Part B template (as a zip file which includes the xls template for the National Budgets Table and the rft template for the Part B)

Yves Gigase KDT-CY workshop, 29 July 2022

PARTNERSHIP

0

24

## **EVALUATION AND SELECTION**

- Evaluation = experts, as in HE

- Selection = by PAB, based on expert ranking, depends on available national budget of all participants in proposal

- Timing = Selection decision end November 2022, GAP till May 2023, start of project.

Yves Gigase KDT-CY workshop, 29 July 2022

25

## What is next?

### A NEW DEVELOPMENT: EUROPEAN CHIPS ACT

EUROPEAN PARTNERSHIP

27

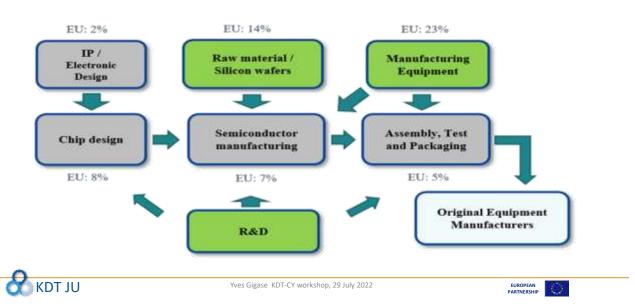

### **SEMICONDUCTORS VALUE CHAIN IN EUROPE**

#### THE EUROPEAN CHIPS ACT

#### 3 Pillars

#### **Chips for Europe Initiative:**

pool resources from EU, MS and other, as well as the private sector, through: the "Chips Joint Undertaking"

New framework to ensure security of supply by:

A. Attracting **investments** and enhanced **production capacities**.

B. Chips Fund to facilitate access to finance for start-ups to help them mature their innovations and attract investors.

C. Dedicated semiconductor equity investment facility under InvestEU to support scale-ups and SMEs to ease their market expansion.

Coordination mechanism between the Member States and the Commission for monitoring the supply of semiconductors, estimating demand and anticipating the shortages.

- monitor the semiconductor value chain

- · common crisis assessment

- coordinate actions to be taken from a new emergency toolbox

- · react swiftly and decisively together

Yves Gigase KDT-CY workshop, 29 July 2022

EUROPEAN PARTNERSHIP

29

29

#### **CHIPS FOR EUROPE INITIATIVE**

Bridge the gap from lab to fab

Create large innovation

capacity and a resilient and

dynamic semiconductor

ecosystem

- Build up large-scale design innovative capacities for integrated semiconductor technologies

- · Enhance existing and developing new pilot lines

- Build advanced technology and engineering capacities for accelerating the development of quantum chips

- Create a network of competence centres across Europe

- Establish a Chips Fund to facilitate access to loans and equity by start-ups, scale-ups and SMEs and other companies in the semiconductor value chains

Basic Research Applied Research

Prototyping

Pilot lines

Production

Yves Gigase KDT-CY workshop, 29 July 2022

## Q&A

- Advice = try to participate in projects under preparation (but already very late)

- Organise the local community, watch out for next call 2023, brokerage event in February 2023

- Good Luck with your application!

- Don't hesitate to contact us

- Please read the documents!

Yves Gigase KDT-CY workshop, 29 July 2022

31